## 200Gb/s QSFP-DD ER4 40km Transceiver

#### **LA-OT-200G-ER4**

#### **Description**

This product is a 200Gb/s Quad Small Form Factor Pluggable-double density (QSFP-DD) optical module designed for optical communication applications. The module converts 8 channels of 25Gb/s (NRZ) electrical input data to 4 channels of LAN-WDM optical signals, and multiplexes them into a single channel for 200Gb/s(PMA4) optical transmission. Reversely, on the receiver side, the module optically de-multiplexes a 200Gb/s(PMA4) optical input into 4 channels of WDM optical signals, and converts them to 8 channels of 25Gb/s (NRZ) electrical output data. The central wavelengths of the 4 LAN WDM channels are 1295.56, 1300.05, 1304.58 and 1309.14 nm as members of the LAN WDM wavelength grid defined in IEEE802.3ba. It contains a duplex LC connector for the optical interface and a 76-pin connector for the electrical interface. To minimize the optical dispersion in the long-haul system, single-mode fiber (SMF) has to be applied in this module. It can support up to 30km with 200G FEC and 40km with built-in PFEC. The product is designed with form factor, optical/electrical connection and digital diagnostic interface according to the QSFP-DD Multi-Source Agreement (MSA). It has been designed to meet the harshest external operating conditions including temperature, humidity and EMI interference.

#### **Features**

- QSFP-DD MSA compliant

- 4 LWDM lanes MUX/DEMUX design

- Up to 40km transmission on single mode fiber (SMF) with built-in PFEC

- Operating case temperature: 0 to 70oC

- Maximum power consumption 12W

- Duplex LC connector

- RoHS compliant

### **Applications**

- 5G Network

- 200G Ethernet

- Enterprise networking

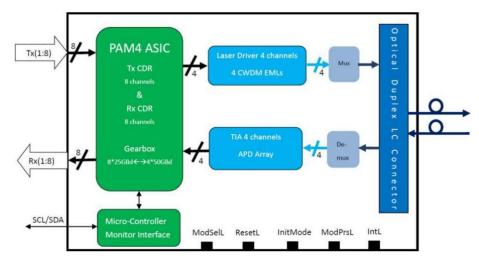

### **Transceiver Block Diagram**

Figure 1. Transceiver Block Diagram

### **Pin Assignment and Description**

The electrical pinout of the QSFP-DD module is shown in Figure 2 below.

Figure 2. MSA Compliant Connector

www.lanaotek.com 2

### **Pin Definition**

| Pin | Logic          | Logic Symbol Description |                                                                                     | Plug Sequence | Notes |  |

|-----|----------------|--------------------------|-------------------------------------------------------------------------------------|---------------|-------|--|

| 1   |                | GND                      | Ground                                                                              | 1B            | 1     |  |

| 2   | CML-I          | Tx2n                     | Transmitter Inverted Data Input                                                     | 3B            |       |  |

| 3   | CML-I          | Тх2р                     | Transmitter Non-Inverted Data Input                                                 | 3B            |       |  |

|     |                |                          |                                                                                     |               |       |  |

| 4   |                | GND                      | Ground                                                                              | 1B            | 1     |  |

| 5   | CML-I          | Tx4n                     | Transmitter Inverted Data Input                                                     | 3B            |       |  |

| 6   | CML-I          | Тх4р                     | Transmitter Non-Inverted Data Input                                                 | 3B            |       |  |

| 7   |                | GND                      | Ground                                                                              | 1B            | 1     |  |

| 8   | LVTTL-I        | ModSelL                  | Module Select                                                                       | 3B            |       |  |

| 9   | LVTTL-I        | ResetL                   | Module Reset                                                                        | 3B            |       |  |

| 10  |                | VccRx                    | +3.3V Power Supply Receiver                                                         | 2B            | 2     |  |

| 11  | LVCMOS-<br>I/O | SCL                      | 2-wire serial interface clock                                                       | 3B            |       |  |

| 12  | LVCMOS-<br>I/O | SDA                      | 2-wire serial interface data                                                        | 3B            |       |  |

| 13  |                | GND                      | Ground                                                                              | 1B            | 1     |  |

| 14  | CML-O          | Rx3p                     | Receiver Non-Inverted Data Output                                                   | 3B            |       |  |

| 15  | CML-O          | Rx3n                     | Receiver Inverted Data Output                                                       | 3B            |       |  |

| 16  | GND            | Ground                   | 1B                                                                                  |               | 1     |  |

| 17  | CML-O          | Rx1p                     | Receiver Non-Inverted Data Output                                                   | 3B            |       |  |

| 18  | CML-O          | Rx1n                     | Receiver Inverted Data Output                                                       | 3B            |       |  |

| 19  |                | GND                      | Ground                                                                              | 1B            | 1     |  |

| 20  |                | GND                      | Ground                                                                              | 1B            | 1     |  |

| 21  | CML-O          | Rx2n                     | Receiver Inverted Data Output                                                       | 3B            |       |  |

| 22  | CML-O          | Rx2p                     | Receiver Non-Inverted Data Output                                                   | 3B            |       |  |

| 23  |                | GND                      | Ground                                                                              | 1B            | 1     |  |

| 24  | CML-O          | Rx4n                     | Receiver Inverted Data Output                                                       | 3B            |       |  |

| 25  | CML-O          | Rx4p                     | Receiver Non-Inverted Data Output                                                   | 3B            |       |  |

| 26  |                | GND                      | Ground                                                                              | 1B            | 1     |  |

| 27  | LVTTL-O        | ModPrsL                  | Module Present                                                                      | 3B            |       |  |

| 28  | LVTTL-O        | IntL                     | Interrupt                                                                           | 3B            |       |  |

| 29  |                | VccTx                    | +3.3V Power supply transmitter                                                      | 2B            | 2     |  |

| 30  |                | Vcc1                     | +3.3V Power supply                                                                  | 2B            | 2     |  |

| 31  | LVTTL-I        | InitMode                 | Initialization mode; In legacy QSFP applications, the InitMode pad is called LPMODE | 3B            |       |  |

| 32  |                | GND                      | Ground                                                                              | 1B            | 1     |  |

| 33  | CML-I          | Тх3р                     | Transmitter Non-Inverted DataInput                                                  | 3B            |       |  |

| 34  | CML-I          | Tx3n                     | Transmitter Inverted Data Input                                                     | 3B            |       |  |

| 35  |                | GND                      | Ground                                                                              | 1B            | 1     |  |

| 36  | CML-I          | Tx1p                     | Transmitter Non-Inverted Data Input                                                 | 3B            |       |  |

3

| 37 | CML-I | Tx1n     | Transmitter Inverted Data Input | 3B |   |

|----|-------|----------|---------------------------------|----|---|

| 38 |       | GND      | Ground                          | 1B | 1 |

| 39 |       | GND      | Ground                          | 1A | 1 |

| 40 | CML-I | Tx6n     | Transmitter Inverted Data Input | 3A |   |

| 41 | CML-I | Тх6р     | Transmitter Non-Inverted Data   | 3A |   |

|    |       |          | Input                           |    |   |

| 42 |       | GND      | Ground                          | 1A | 1 |

| 43 | CML-I | Tx8n     | Transmitter Inverted Data Input | 3A |   |

| 44 | CML-I | Тх8р     | Transmitter Non-Inverted Data   | 3A |   |

|    |       |          | Input                           |    |   |

| 45 |       | GND      | Ground                          | 1A | 1 |

| 46 |       | Reserved | For future use                  | 3A | 3 |

| 47 |       | VS1      | Module Vendor Specific 1        | 3A | 3 |

| 48 |       | VccRx1   | 3.3V Power Supply               | 2A | 2 |

| 49 |       | VS2      | Module Vendor Specific 2        | 3A | 3 |

| 50 |       | VS3      | Module Vendor Specific 3        | 3A | 3 |

| 51 |       | GND      | Ground                          | 1A | 1 |

| 52 | CML-O | Rx7p     | Receiver Non-Inverted Data      | 3A |   |

|    |       |          | Output                          |    |   |

| 53 | CML-O | Rx7n     | Receiver Inverted Data Output   | 3A |   |

| 54 |       | GND      | Ground                          | 1A | 1 |

| 55 | CML-O | Rx5p     | Receiver Non-Inverted Data      | 3A |   |

|    |       |          | Output                          |    |   |

| 56 | CML-O | Rx5n     | Receiver Inverted Data Output   | 3A |   |

| 57 |       | GND      | Ground                          | 1A | 1 |

| 58 |       | GND      | Ground                          | 1A | 1 |

| 59 | CML-O | Rx6n     | Receiver Inverted Data Output   | 3A |   |

| 60 | CML-O | Rx6p     | Receiver Non-Inverted Data      | 3A |   |

|    |       |          | Output                          |    |   |

| 61 |       | GND      | Ground                          | 1A | 1 |

| 62 | CML-O | Rx8n     | Receiver Inverted Data Output   | 3A |   |

4

| 63 | CML-O | Rx8p     | Receiver Non-Inverted Data      | 3A |   |

|----|-------|----------|---------------------------------|----|---|

|    |       |          | Output                          |    |   |

| 64 |       | GND      | Ground                          | 1A | 1 |

| 65 |       | NC       | No Connect                      | 3A | 3 |

| 66 |       | Reserved | For future use                  | 3A | 3 |

| 67 |       | VccTx1   | 3.3V Power Supply               | 2A | 2 |

| 68 |       | Vcc2     | 3.3V Power Supply               | 2A | 2 |

| 69 |       | Reserved | For Future Use                  | 3A | 3 |

| 70 |       | GND      | Ground                          | 1A | 1 |

| 71 | CML-I | Тх7р     | Transmitter Non-Inverted        | 3A |   |

|    |       |          | DataInput                       |    |   |

| 72 | CML-I | Tx7n     | Transmitter Inverted Data Input | 3A |   |

| 73 |       | GND      | Ground                          | 1A | 1 |

| 74 | CML-I | Тх5р     | Transmitter Non-Inverted        | 3A |   |

|    |       |          | DataInput                       |    |   |

| 75 | CML-I | Tx5n     | Transmitter Inverted Data Input | 3A |   |

| 76 |       | GND      | Ground                          | 1A | 1 |

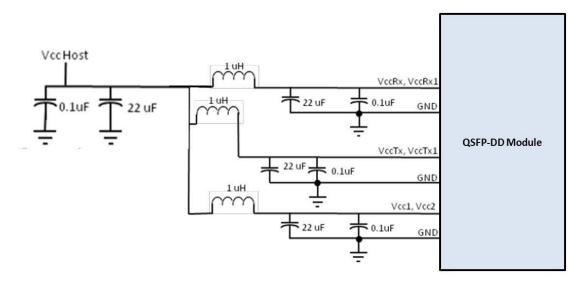

## **Recommended Power Supply Filter**

Figure 3. Recommended Power Supply Filter

5

### **Absolute Maximum Ratings**

It has to be noted that the operation in excess of any individual absolute maximum ratingsmight cause permanent damage to this module.

| Parameter                            | Symbol | Min  | Max | Units | Notes |

|--------------------------------------|--------|------|-----|-------|-------|

| Storage Temperature                  | TS     | -40  | 85  | degC  |       |

| Operating Case Temperature           | ТОР    | 0    | 70  | degC  |       |

| Power Supply Voltage                 | VCC    | -0.5 | 3.6 | V     |       |

| Relative Humidity (non-condensation) | RH     | 0    | 85  | %     |       |

| Damage Threshold, each Lane          | THd    | -5.0 |     | dBm   |       |

### **Recommended Operating Conditions and Power Supply Requirements**

| Parameter                  | Symbol | Min   | Typical | Max                  | Units | Notes |

|----------------------------|--------|-------|---------|----------------------|-------|-------|

| Operating Case Temperature | ТОР    | 0     |         | 70                   | degC  |       |

| Power Supply Voltage       | VCC    | 3.135 | 3.3     | 3.465                | V     |       |

| Data Rate, each Lane       |        |       | 26.5625 |                      | GBd   | PAM4  |

| Data Rate Accuracy         |        | -100  |         | 100                  | ppm   |       |

| Pre-FEC Bit Error Ratio    |        |       |         | 2.4x10 <sup>-4</sup> |       |       |

| Post-FEC Bit Error Ratio   |        |       |         | 1x10 <sup>-12</sup>  |       | 1     |

| Link Distance              | D      | 0.002 |         | 30                   | km    | 2     |

| Link Distance              | D      | 0.002 |         | 40                   | Km    | 3     |

#### Notes:

- 1. FEC provided by host system.

- 2. FEC required on host system to support maximum distance.

- 3. Built-in PFEC is required to support up to  $40\mbox{km}$

#### **Electrical Characteristics**

The following electrical characteristics are defined over the Recommended Operating Environment unless otherwise specified.

| Parameter                                        | Test<br>Point | Min                                        | Typical      | Max  | Units | Notes |

|--------------------------------------------------|---------------|--------------------------------------------|--------------|------|-------|-------|

| Power Consumption                                |               |                                            |              | 12   | W     |       |

| Supply Current                                   | Icc           |                                            |              | 3.64 | Α     |       |

|                                                  | Transı        | mitter (each Lan                           | e)           |      |       |       |

| Signaling Rate, each Lane                        | TP1           | 26.562                                     | 25 ± 100 ppm | 1    | GBd   |       |

| Differential pk-pk Input<br>Voltage Tolerance    | TP1a          | 900                                        |              |      | mVpp  | 1     |

| Differential Termination Mismatch                | TP1           |                                            |              | 10   | %     |       |

| Differential Input Return Loss                   | TP1           | IEEE 802.3-<br>2015<br>Equation<br>(83E-5) |              |      | dB    |       |

| Differential to Common<br>Mode Input Return Loss | TP1           | IEEE 802.3-<br>2015<br>Equation<br>(83E-6) |              |      | dB    |       |

| Module Stressed Input Test                       | TP1a          | See IEEE 802.3bs 120E.3.4.1                |              |      |       | 2     |

| Single-ended Voltage Tolerance Range (Min)       | TP1a          |                                            | -0.4 to 3.3  |      | V     |       |

| DC Common Mode Input<br>Voltage                  | TP1           | -350                                       |              |      |       | 2850  |

|                                                  | Rece          | eiver (each Lane)                          | )            |      |       |       |

| Signaling Rate, each lane                        | TP4           | 26.562                                     | 25 ± 100 ppm | 1    | GBd   |       |

| Differential Peak-to-Peak Output Voltage         | TP4           |                                            |              |      |       | 900   |

| AC Common Mode Output<br>Voltage, RMS            | TP4           |                                            |              |      |       | 17.5  |

| Differential Termination  Mismatch               | TP4           |                                            |              |      |       | 10    |

|                                           |     | IEEE 802.3- |       |      |

|-------------------------------------------|-----|-------------|-------|------|

| Differential Output ReturnLoss            | TP4 | 2015        |       |      |

|                                           |     | Equation    |       |      |

|                                           |     | (83E-2)     |       |      |

| Common to Differential                    |     | IEEE 802.3- |       |      |

| Mode Conversion ReturnLoss                | TP4 | 2015        |       |      |

| ivioue conversion Returnloss              |     | Equation    |       |      |

|                                           |     | (83E-3)     |       |      |

| Transition Time, 20% to 80%               | TP4 | 9.5         |       |      |

| Near-end Eye Symmetry Mask Width (ESMW)   | TP4 |             | 0.265 |      |

| Near-end Eye Height, Differential         | TP4 | 70          |       |      |

| Far-end Eye Symmetry Mask<br>Width (ESMW) | TP4 |             | 0.2   |      |

| Far-end Eye Height, Differential          | TP4 | 30          |       |      |

| Far-end Pre-cursor ISI Ratio              | TP4 | -4.5        |       | 2.5  |

| Common Mode Output<br>Voltage (Vcm)       | TP4 | -350        |       | 2850 |

| -                                         |     |             |       |      |

#### Notes:

- 1. With the exception to IEEE 802.3bs 120E.3.1.2 that the pattern is PRBS31Q or scrambled idle.

- 2. Meets BER specified in IEEE 802.3bs 120E.1.1.

- 3. DC common mode voltage generated by the host. Specification includes effects of ground offset voltage.

# **Optical Characteristics**

| Parameter                       | Symbol | Min              | Typical                   | Max     | Units | Notes |

|---------------------------------|--------|------------------|---------------------------|---------|-------|-------|

|                                 | LO     | 1294.53          | 1295.56                   | 1296.59 | nm    |       |

| Wavelength Assignment           | L1     | 1299.02          | 1300.05                   | 1301.09 | nm    |       |

|                                 | L2     | 1303.54          | 1304.58                   | 1305.63 | nm    |       |

|                                 | L3     | 1308.09          | 1309.14                   | 1310.19 | nm    |       |

|                                 | Tra    | nsmitter         | L                         |         |       | L     |

| Data Rate, each Lane            |        | 53               | .125 ± 100 p <sub>l</sub> | om      | GBd   |       |

| Modulation Format               |        |                  | PAM4                      |         |       |       |

| Side-mode Suppression Ratio     | SMSR   | 30               |                           |         | dB    |       |

| Total Average Launch Power      | PT     |                  |                           | 14.7    | dBm   |       |

| Average Launch Power, each Lane | PAVG   | -0.1             |                           | 5.6     | dBm   |       |

| Outer Optical Modulation        | РОМА   | 3.4              |                           | 6.4     | dBm   |       |

| Amplitude (OMAouter), each Lane | TOWA   | 3.4              |                           | 0.4     | abiii |       |

| Launch Power in OMAouter minus  |        | 3                |                           |         | dB    |       |

| TDECQ, each Lane                |        |                  |                           |         | ub.   |       |

| Transmitter and Dispersion Eye  | TDECQ  |                  |                           | 3.2     | dB    |       |

| Closure for PAM4, each Lane     |        |                  |                           |         |       |       |

| Extinction Ratio                | ER     | 6                |                           |         | dB    |       |

| Difference in Launch Power      |        |                  |                           |         |       |       |

| between any Two Lanes           |        |                  |                           | 4       | dB    |       |

| (OMA <sub>outer</sub> )         |        |                  |                           |         |       |       |

| RIN15.10MA                      | RIN    | -132             |                           |         | dB/Hz |       |

| Optical Return Loss Tolerance   | TOL    |                  |                           | 15.1    | dB    |       |

| Transmitter Reflectance         | RŢ     |                  |                           | -26     | dB    |       |

| Average Launch Power of OFF     | Poff   |                  |                           | -30     | dBm   |       |

| Transmitter, each Lane          |        |                  |                           |         | 25    |       |

|                                 | R      | eceiver          |                           |         |       |       |

| Data Rate, each Lane            |        | 53.125 ± 100 ppm |                           |         | GBd   |       |

| Modulation Format               |        |                  | PAM4                      |         |       |       |

www.lanaotek.com 9

| Sensitivity, each lane                                       | Sen1 | MAX (-11.1, SECQ-12.5) |     |  | dBm | For<br>30km |  |  |  |

|--------------------------------------------------------------|------|------------------------|-----|--|-----|-------------|--|--|--|

| Sensitivity, each lane                                       | Sen2 | MAX (-14.1, SECQ-15.5) |     |  | dBm | For 40km    |  |  |  |

| Stressed Conditions for Stress Receiver Sensitivity (Note 8) |      |                        |     |  |     |             |  |  |  |

| Stressed Eye Closure for PAM4 (SECQ), Lane under Test        |      |                        | 3.4 |  | dB  |             |  |  |  |

| SECQ – 10*log10(Ceq), Lane underTest                         |      |                        |     |  | dB  |             |  |  |  |

| OMA <sub>outer</sub> of each Aggressor Lane                  |      |                        | -8  |  | dBm | _           |  |  |  |

# **Digital Diagnostic Functions**

| Parameter                | Symbol       | Min  | Max | Units | Notes               |

|--------------------------|--------------|------|-----|-------|---------------------|

| Temperature Monitor      |              |      |     |       | Over operating      |

| Absolute Error           | DMI_Temp     | -3   | 3   | degC  | temperature range   |

| Supply Voltage Monitor   | DMI_VCC      | -0.1 | 0.1 | V     | Over full operating |

| Absolute Error           |              |      |     |       | range               |

| Channel RX Power Monitor |              |      |     |       |                     |

| Absolute Error           | DMI_RX_Ch    | -2   | 2   | dB    | 1                   |

| Channel Bias Current     | DMI_lbias_Ch | -10% | 10% | mA    |                     |

| Monitor                  |              |      |     |       |                     |

| Channel TX Power Monitor | DMI_TX_Ch    | -2   | 2   | dB    | 1                   |

| Absolute Error           |              |      |     |       |                     |

The following digital diagnostic characteristics are defined over the normal operating conditions unless otherwise specified.

#### Notes:

4. Due to measurement accuracy of different single mode fibers, there could be an additional +/-1 dB fluctuation, or a +/- 3 dB total accuracy.

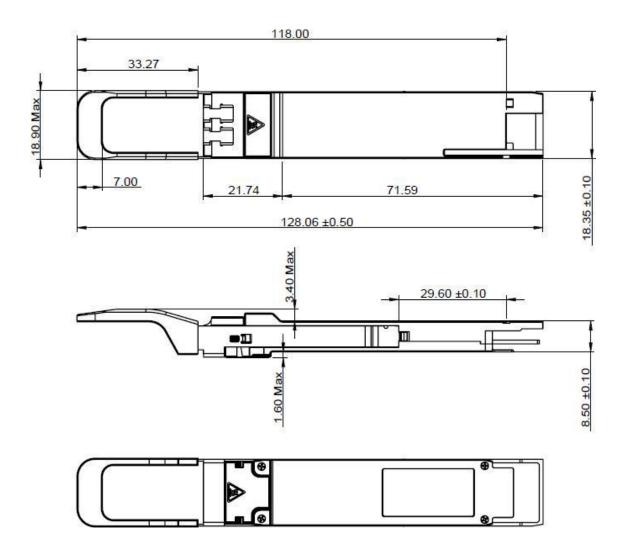

# **Outline Drawing (mm)**

## https://www.lanaotek.com

Specifications & design are subject to change without prior notice.

For more details, please email to info@lanaotek.com. Copyright©2024 lanaotek.com All Rights Reserved